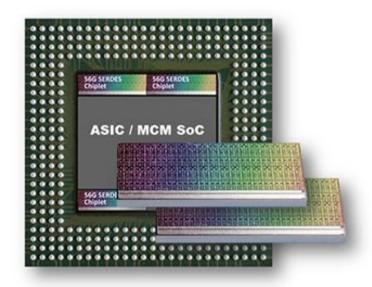

Credo は、新しい 3.2Tbps BlueJay リタイマーチップレット生産供給を発表した。BlueJay は、64 レーンの 56Gbps PAM4 LR DSP 接続でロバストなシステムレベル接続を提供する。新しいデバイスは、次世代マルチチップモジュール(MCM) ASICs に低消費電力、システム距離性能を提供するものである。これらは、先進的スイッチング、ハイパフォーマンスコンピューティング(HPC)、人工知能(AI)、マシンラーニングアプリケーションで使用される。

BlueJay は、ホストサイドで、超低消費電力バンチ・オブ・ワイヤ (BoW) ダイ・ツー・ダイ (die-to-die) インタフェースを使い、MCM SoC(system-on-chip)コアと通信する。ワイドバス BoW インタフェースは、TSMC CoWoS パッケージングに最適化されている。これは、ハイパフォーマンスコンピューティング (HPC)アプリケーション向けに設計されたものである。ラインサイドでは、チップレットは、64 レーンの低消費電力 56G PAM4 LR SerDes を持ち、MCM にロバスト、オフパッケージインタフェースを提供。これにより、様々なシステムレベル構成で組込が容易になる。

「チップレット組込により、顧客は、向上したパフォーマンスで ASIC を加速 することができ、先進的なスイッチング、ストレージ、HPC、AI、マシンラー ニング、およびサービスプロバイダアプリケーションをサポートできる。こ れらデータ集約的アプリケーションは、次世代 ASICs に広範な構造的要求を 課す」と Credo のワールドワイド販売担当 VP、Michael Girvan Lampe は、 コメントしている。

「BlueJay は、今年製造に入る第2の Credo 3.2Tbps リタイマである。 Credo のシリコンで実証済みのチップレット全て、56G および 112G レーンレート と SerDes DSP IP は、Time to Market と性能目的を達成するために ASIC デザイナに多様なオプションを提供する」(Lampe)。

Credo 独自の SerDes 技術により BlueJay チップレットは、高価な先端プロセス技術で製造される競合ソリューションに対して、TSMC 28nm プロセスで製造でき、重要なパフォーマンスと低消費電力要求の期待に沿うものである。Credo の最適化されたデバイスアーキテクチャにより電力効率の優れた BoW インタフェースの利用が可能になり、ASIC からの SerDes オフロードを容易にし、MCM SoC へのその組込を簡素化する。

MCM 設計へのチップレット組込は、ASIC イノベーションとシステム展開を加速する。これは、ネットワークサービスプロバイダやハイパースケールデータセンタの増え続ける性能要求に応えるものである。オンダイ SerDes機能をオフチップに移行することで、ASIC ダイエリアの最大 30%が、追加コンピュート、増大したスイッチングパフォーマンス、より深いルーティングテーブルなどの機能に転用可能になる。

「ネットワーキングとデータセンタアーキテクチャは、400Gbps から 800Gbps、それ以上へ、そのインフラストラクチャを移行しつつある。より高いパフォーマンス、デジタルコアとアナログインタエェース機能を統合した低消費電力 ASICs を必要としている」と、650 グループ創始者、技術アナリスト、Alan Weckel は指摘している。「しかし、モノリシック ASIC コンポーネントで性能を達成することは、難しい。アナログとデジタルのプロセスノードの進歩速度が違うからである。Credo のリタイマチップレットを使うマルチチップモジュールは、アナログインタフェースをデジタルコア ASIC から分離し、コストを下げ、リスクを低減し、加速度的移行サイクルを可能にする」と同氏はコメントしている。